Podczas konferencji Hot Chips 33, AMD zaprezentowało swoje rozwiązanie 3D V-Cache, które ma być krokiem milowym w rozwoju ich procesorów z architekturą Zen, ale nie tylko.

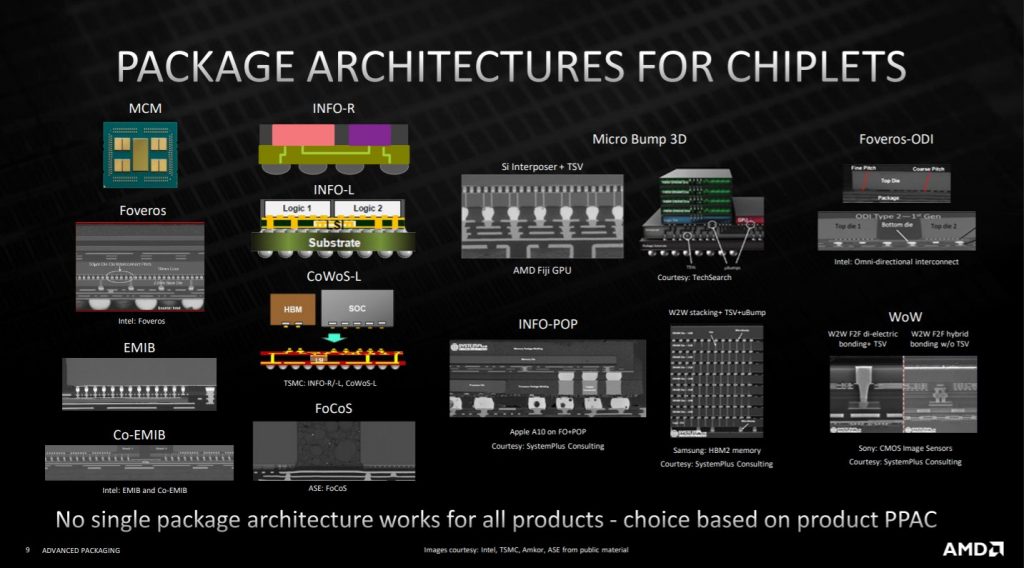

Prezentacja AMD pozwoliła nam przypomnieć sobie o wszystkich tego typu technologiach, które pozwalają na układanie stosów z układów scalonych, Aktualnie najbardziej popularnym sposobem łączenia poszczególnych warstw niezależnie w procesorach, czy w modułach pamięci jest TSV (Through Silicon Via). To technika łączenia poszczególnych warstw przy użyciu mikro-połączeń (mostów) i to od liczby tego typu połączeń uzależniona jest szybkość transmisji i jej stabilność.

Rozwiązanie AMD w przypadku połączeń TSV to stosowanie połączeń o odstępie 9 mikronów ma ono być konkurencyjne do techniki Intel Foveros Direct, która bazuje na połączeniach o odstępach 10 mikronów.

AMD przewiduje, że ich najnowsza technika 3D Chiplet, stosująca połączenia 9 mikronów, będzie 3 razy wydajniejsza energetycznie i gęstość połączeń wzrośnie piętnastokrotnie.

Pierwszymi procesorami, które miałyby skorzystać z tego typu układania stosów z układów półprzewodnikowych, miałyby być procesory AMD wykorzystujące architekturę Zen3, a dokładnie AMD Ryzen 9 5900X, który ma otrzymać większą o 64 MB pamięć podręczną L3.